- Verilog | D触发器

- Verilog | D触发器(1)

- Verilog | JK触发器(1)

- Verilog | JK触发器

- Verilog D闩锁

- Verilog D闩锁(1)

- Verilog数组

- Verilog数组(1)

- Verilog函数(1)

- Verilog函数

- Verilog模块

- Verilog模块(1)

- Verilog参数(1)

- Verilog参数

- Verilog运算符(1)

- Verilog运算符

- Verilog教程

- Verilog块语句(1)

- Verilog块语句

- Verilog端口

- Verilog端口(1)

- 触发器 - SQL (1)

- SQL |触发器(1)

- SQL |触发器

- Verilog分配

- Verilog分配(1)

- Verilog 数据类型

- Verilog数据类型

- Verilog数据类型(1)

📅 最后修改于: 2021-01-11 15:08:19 🧑 作者: Mango

T字拖鞋

T代表(“ toggle”)触发器,以避免SR触发器处于中间状态。我们应该仅向触发器提供一个输入,称为触发输入切换输入,以避免发生中间状态。

然后,触发器充当Toggle开关。下一个输出状态通过当前状态输出的补码来更改。此过程称为“切换” 。

我们可以通过更改JK触发器来构造T触发器。 T型触发器只有一个输入,它是通过连接JK触发器的输入构成的。此单个输入称为T。

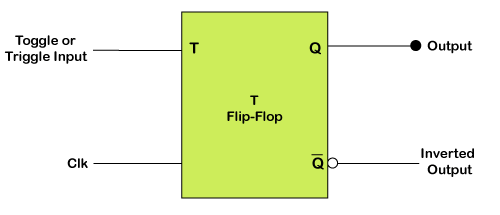

T触发器的框图如下所示,其中T定义“切换”输入,而CLK定义“时钟信号”输入。

T触发器电路

有两种形成T型触发器的方法:

- 通过将输出反馈连接到“ SR触发器”中的输入。

- 我们将执行T和Q PREV输出的XOR操作后获得的输出作为D触发器中的D输入。

施工

T触发器的设计绕过了AND门的输出,作为SR触发器NOR门的输入。 “与”门的输入,当前输出状态Q及其补码Q'发送回每个“与”门。

切换输入作为输入传递到AND门。这些门连接到时钟(CLK)信号。在T型触发器中,几乎没有触发的脉冲序列作为触发器输入传递,它改变了触发器的输出状态。使用SR触发器的T触发器的电路图如下:

使用D触发器形成T触发器。在D触发器中,将T输入与输出“ QPREV”执行XOR操作后的输出作为D输入传递。使用D触发器的T触发器的逻辑电路如下:

D触发器的最简单结构是JK触发器。两个JK触发器输入都作为单个输入T连接。以下是由JK触发器组成的T触发器的逻辑电路:

T触发器真相表

当输出Q To设置为0时,启用上层NAND门,禁用下层NAND门。将触发器置于“设置状态(Q = 1)”,触发器将通过触发器中的S输入。

当输出Q设置为1时,将禁用上级NAND门,并启用下级NAND门。触发器将触发器中的R输入传递给触发器,使触发器处于“复位状态(Q = 0)”。

T型触发器的操作

当T输入设置为false或0时,T触发器的下一个状态类似于当前状态。

- 如果切换输入设置为0并且当前状态也为0,则下一个状态将为0。

- 如果切换输入设置为0并且当前状态为1,则下一个状态将为1。

当触发器输入设置为1时,触发器的下一个状态与当前状态相反。

- 如果切换输入设置为1并且当前状态为0,则下一个状态将为1。

- 如果切换输入设置为1并且当前状态为1,则下一个状态将为0。

当输入触发器交替更改设置和复位输入时,将切换T触发器。 T型触发器需要两个触发器来完成输出波形的整个周期。

T触发器产生的输出频率是输入频率的一半。 T触发器用作“分频器电路”。

在T触发器中,仅在定义了先前状态时才定义施加的触发脉冲的状态。这是T型触发器的主要缺点。

由于T触发器不可用作IC,因此可以从“ JK触发器”,“ SR触发器”和“ D触发器”设计T触发器。下面给出了使用“ JK触发器”的T触发器的框图:

例

module tff ( input clk, input rstn, input t, output reg q);

always @ (posedge clk) begin

if (!rstn)

q <= 0;

else

if (t)

q <= ~q;

else

q <= q;

end

endmodule

试验台

module tb;

reg clk;

reg rstn;

reg t;

tff u0 ( .clk(clk),

.rstn(rstn),

.t(t),

.q(q));

always #5 clk = ~clk;

initial begin

{rstn, clk, t} <= 0;

$monitor ("T=%0t rstn=%0b t=%0d q=%0d", $time, rstn, t, q);

repeat(2) @(posedge clk);

rstn <= 1;

for (integer i = 0; i < 20; i = i+1) begin

reg [4:0] dly = $random;

#(dly) t <= $random;

end

#20 $finish;

end

endmodule