📌 相关文章

- 实施Full Adder的Python程序

- 实施Full Adder的Python程序(1)

- D3.js Adder() 方法

- D3.js Adder() 方法(1)

- Verilog D闩锁

- Verilog D闩锁(1)

- Verilog数组

- Verilog数组(1)

- Verilog函数

- Verilog函数(1)

- Python中的 numpy.full()

- Python中的 numpy.full()(1)

- Verilog模块

- Verilog模块(1)

- Verilog参数(1)

- Verilog参数

- Verilog运算符

- Verilog运算符(1)

- Verilog教程

- Verilog块语句(1)

- Verilog块语句

- Verilog端口(1)

- Verilog端口

- Verilog分配

- Verilog分配(1)

- Verilog数据类型

- Verilog数据类型(1)

- Verilog 数据类型

- Verilog 数据类型(1)

📜 Verilog Full Adder

📅 最后修改于: 2021-01-11 15:17:48 🧑 作者: Mango

Verilog Full Adder

全加法器是一个数字组件,它执行三个数字,并使用逻辑门实现。它是处理器ALU中的主要组件,用于增加地址,表索引,缓冲区指针和其他需要加法的位置。

1位全加法器将3个1位二进制数,2个输入位,1个进位位相加,并输出总和和一个进位位。

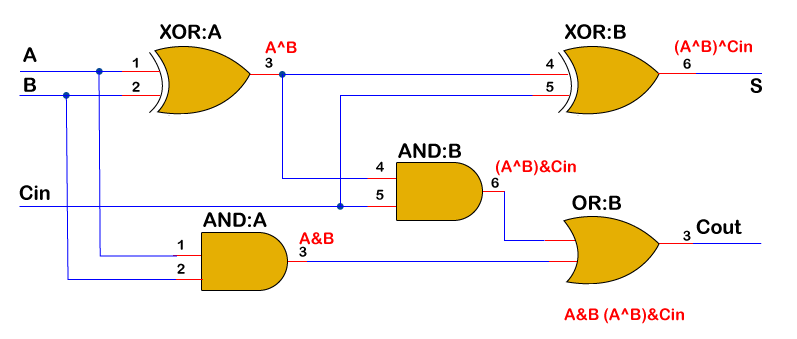

通过使用两个半加器并对它们的最终输出进行“或”运算,形成一个完整的加法器。半加法器将两个二进制数相加。完整的加法器是组合电路,因此可以用Verilog语言建模。

下面给出两个输出总和和进位的逻辑表达式。 A,B是两位二进制数的输入变量,Cin是进位输入,而Cout是Sum和Carry的输出变量。

真相表

| A | B | Cin | Cout | Sum |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

例

下面显示了一个4位加法器的示例,该加法器通过信号a和b接受两个二进制数。

加法器是组合电路。因此,Verilog可以使用带有分配的连续分配或带有包含所有输入的敏感度列表的Always Block对其进行建模。

module fulladder ( input [3:0] a,

input [3:0] b,

input c_in,

output c_out,

output [3:0] sum);

assign {c_out, sum} = a + b + c_in;

endmodule

下面的代码显示了always块的使用,只要其任何输入更改值,该块就会执行。

module fulladder ( input [3:0] a,

input [3:0] b,

input c_in,

output reg c_out,

output reg [3:0] sum);

always @ (a or b or c_in) begin

{c_out, sum} = a + b + c_in;

end

endmodule

硬件原理图

试验台

首先,添加时间刻度指令。它以重音符号`开头,但不以分号结尾。 Timescale指令用于指定其他模块中使用的时间单位和时间分辨率(一皮秒)。时间分辨率是精度因子,它决定模块中时间单位的准确性。

接下来是模块和变量声明。

- 寄存器(reg)类型会保留该值,直到下一个值由时钟脉冲驱动到该值为止,并且始终处于初始状态或始终处于阻塞状态。它用于对输入施加刺激。

- 电线(wire)被声明为被动变量。它们的值不会更改,也不能在内部分配它们,始终是一个初始块。

然后是模块实例化。

- 测试台对被测设备(DUT)施加激励。 DUT必须在测试平台下实例化。端口映射是测试平台模块与设计模块模块的链接。

- 现在,我们将对输入变量进行初始激励。这是在初始块下完成的。

- 我们也可以使用$ finish在前面提到的延迟时间内停止仿真。

不同的是使用两个系统任务:

- $ dumpfile用于将网络更改和寄存器的值转储到VCD文件(值更改转储文件)中。

- $ dumpvars用于指定应在filename参数指定的文件名中转储哪些变量。

- 现在,取决于用户是否要在TCL控制台上显示模拟结果。我们使用了$ monitor ,它在信号值改变时显示信号的值。

- 它在always块中执行,敏感性列表与上一节中所述的相同。

- 格式说明符%t为我们提供了当前的模拟时间,而%d用于显示变量的值(以十进制表示)。

module tb_fulladd;

// 1. Declare testbench variables

reg [3:0] a;

reg [3:0] b;

reg c_in;

wire [3:0] sum;

integer i;

// 2. Instantiate the design and connect to testbench variables

fulladd fa0 ( .a (a),

.b (b),

.c_in (c_in),

.c_out (c_out),

.sum (sum));

// 3. Provide stimulus to test the design

initial begin

a <= 0;

b <= 0;

c_in <= 0;

$monitor ("a=0x%0h b=0x%0h c_in=0x%0h c_out=0x%0h sum=0x%0h", a, b, c_in, c_out, sum);

// Use a for loop to apply random values to the input

for (i = 0; i < 5; i = i+1) begin

#10 a <= $random;

b <= $random;

c_in <= $random;

end

end

endmodule

当a和b相加得到大于4位宽的数字时,总和翻转为零,c_out变为1。例如,以黄色突出显示的行相加得到0x11,而低4位被分配给sum和位4到c_out。