数字逻辑中的同步时序电路

解决问题的步骤:

1.从问题陈述或给定的状态表中画出状态图。

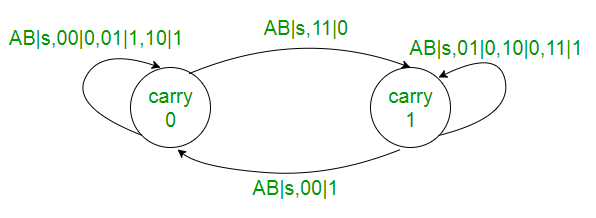

示例:串行加法器。

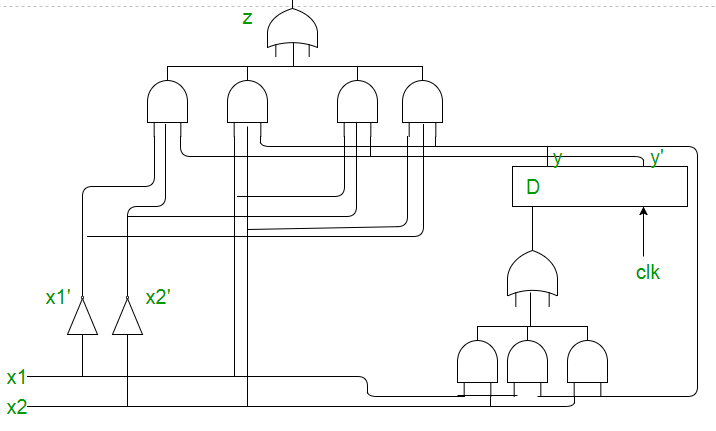

串行加法器的功能可以用下面的状态图来描述。 X1 和 X2 是输入,A 和 B 是表示进位的状态。

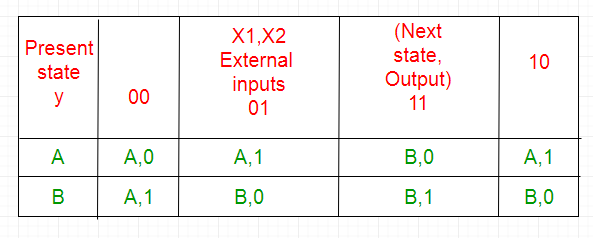

2.画出状态表。如果有任何冗余状态,则减少状态表。  3.选择状态分配,即根据状态总数为状态分配二进制数。还要决定电路的存储元件(触发器)。

3.选择状态分配,即根据状态总数为状态分配二进制数。还要决定电路的存储元件(触发器)。

A -> 0

B -> 1

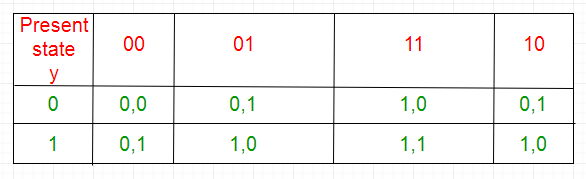

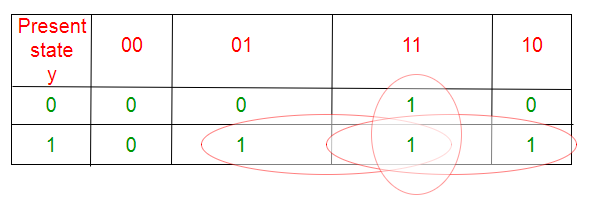

4 、替换状态表中的赋值,得到Transition表:  5.将输出表与转移表分开。

5.将输出表与转移表分开。

z = x 1 x' 2 y+x' 1 x 2 y'+x 1 x 2 y+x 1 x' 2 y'

D触发器的激励表:

D = x 1 x 2 +x 1 y+x 2 y

本文由Kriti Kushwaha提供

如果您发现任何不正确的地方,或者您想分享有关上述主题的更多信息,请写评论。