- 时序电路(1)

- 时序电路

- 时序电路介绍

- 时序电路介绍(1)

- 数字逻辑中的同步时序电路(1)

- 数字逻辑中的同步时序电路

- 异步时序电路

- 异步时序电路

- 异步时序电路(1)

- 时序电路的VHDL编程

- 时序电路的VHDL编程(1)

- 组合和时序电路的分析与设计

- 组合和时序电路的分析与设计(1)

- 组合和时序电路的分析与设计

- 组合和时序电路的分析与设计(1)

- 组合电路和时序电路的区别(1)

- 组合电路和时序电路的区别

- 组合电路和时序电路的区别(1)

- 组合电路和时序电路的区别

- 组合电路和时序电路的区别

- 组合电路和时序电路的区别(1)

- 同步和异步时序电路之间的区别

- 同步和异步时序电路之间的区别(1)

- 同步和异步时序电路之间的区别

- 同步和异步时序电路之间的区别(1)

- 同步和异步时序电路之间的区别

- 是数字 c# (1)

- 数字(1)

- 数字

📅 最后修改于: 2021-01-08 05:52:20 🧑 作者: Mango

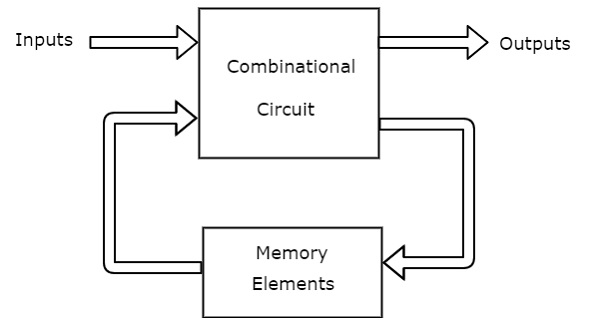

我们在前面的章节中讨论了各种组合电路。所有这些电路都有一组输出,这些输出仅取决于当前输入的组合。下图显示了时序电路的框图。

该时序电路包含一组输入和输出。时序电路的输出不仅取决于当前输入的组合,还取决于先前的输出。先前的输出仅是当前状态。因此,顺序电路包含组合电路以及存储(存储)元件。一些顺序电路可能不包含组合电路,而仅包含存储元件。

下表显示了组合电路和顺序电路之间的区别。

| Combinational Circuits | Sequential Circuits |

|---|---|

| Outputs depend only on present inputs. | Outputs depend on both present inputs and present state. |

| Feedback path is not present. | Feedback path is present. |

| Memory elements are not required. | Memory elements are required. |

| Clock signal is not required. | Clock signal is required. |

| Easy to design. | Difficult to design. |

时序电路的类型

以下是两种类型的时序电路-

- 异步时序电路

- 同步时序电路

异步时序电路

如果时序电路的某些或全部输出相对于时钟信号的有效跃迁不发生变化(影响),则该时序电路称为“异步时序电路” 。这意味着异步时序电路的所有输出不会同时更改(影响)。因此,大多数异步时序电路的输出的不同步与仅任一正沿或时钟信号的只有负边缘。

同步时序电路

如果时序电路的所有输出都相对于时钟信号的有效跃迁发生变化(影响),则该时序电路称为同步时序电路。这意味着同步时序电路的所有输出都同时改变(影响)。因此,同步时序电路的输出仅与时钟信号的正沿或负沿同步。

时钟信号和触发

在本节中,让我们讨论时钟信号和一次触发的类型。

时钟信号

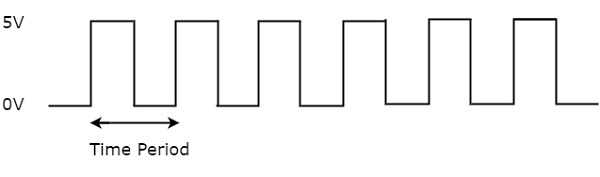

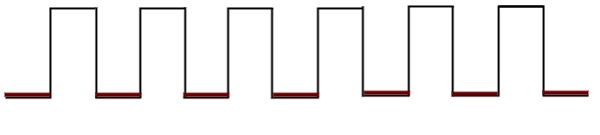

时钟信号是周期信号,其开启时间和关闭时间不必相同。当时钟信号的打开时间和关闭时间相同时,我们可以将时钟信号表示为方波。该时钟信号如下图所示。

在上图中,方波被视为时钟信号。该信号在逻辑高电平(5V)上保持一段时间,并在逻辑低电平(0V)上保持相等的时间。此模式会重复一段时间。在这种情况下,时间段等于开启时间的两倍或关闭时间的两倍。

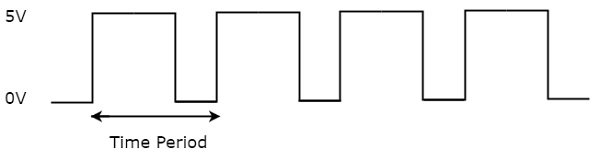

当开启时间和关闭时间不同时,我们可以将时钟信号表示为脉冲序列。该时钟信号如下图所示。

在上图中,脉冲序列被视为时钟信号。该信号保持逻辑高电平(5V)一段时间,并保持逻辑低电平(0V)一段时间。此模式会重复一段时间。在这种情况下,时间段将等于开启时间和关闭时间之和。

时钟信号的时间周期的倒数称为时钟信号的频率。所有时序电路均使用时钟信号进行操作。因此,必须选择顺序电路可以据此操作的频率,时钟信号频率。

触发类型

以下是顺序电路中使用的两种可能的触发类型。

- 电平触发

- 边缘触发

电平触发

时钟信号有两个级别,即逻辑高和逻辑低。以下是两种类型的电平触发。

- 正电平触发

- 负电平触发

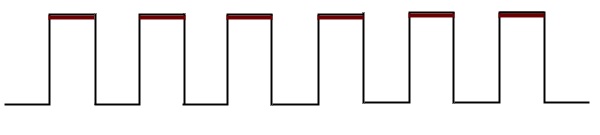

如果时序电路在逻辑高电平时使用时钟信号进行操作,则这种类型的触发称为正电平触发。下图突出显示。

如果时序电路处于“逻辑低”状态时使用时钟信号对其进行操作,则该类型的触发称为负电平触发。下图中突出显示了它。

边缘触发

时钟信号中发生两种类型的转换。这意味着时钟信号从逻辑低转换为逻辑高,或者从逻辑高转换为逻辑低。

以下是基于时钟信号转换的两种类型的边沿触发。

- 上升沿触发

- 负边沿触发

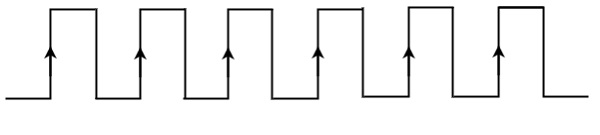

如果时序电路使用从逻辑低电平转换为逻辑高电平的时钟信号进行操作,则这种类型的触发称为正边沿触发。也称为上升沿触发。如下图所示。

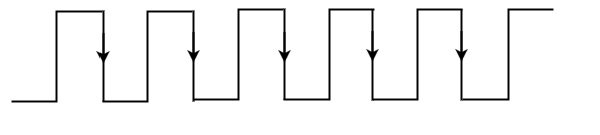

如果时序电路使用从逻辑高电平过渡到逻辑低电平的时钟信号进行操作,则这种类型的触发称为负边沿触发。也称为下降沿触发。如下图所示。

在接下来的章节中,我们将基于可用于其中的触发类型,讨论各种时序电路。