📌 相关文章

- Verilog 4位计数器(1)

- Verilog 4位计数器

- 数字逻辑中的环形计数器

- 数字逻辑中的环形计数器

- 数字逻辑中的环形计数器(1)

- Verilog Mod-N计数器

- Verilog Mod-N计数器(1)

- 数字电子产品中的环形计数器(1)

- 数字电子产品中的环形计数器

- Mod 2 环形计数器(带 D 触发器)

- Mod 2 环形计数器(带 D 触发器)(1)

- Mod 2 环形计数器(带 D 触发器)(1)

- Mod 2 环形计数器(带 D 触发器)

- Verilog灰色计数器

- Verilog灰色计数器(1)

- Verilog波纹计数器(1)

- Verilog波纹计数器

- Verilog D闩锁

- Verilog D闩锁(1)

- Verilog Johnson计数器(1)

- Verilog Johnson计数器

- Verilog数组

- Verilog数组(1)

- Verilog函数

- Verilog函数(1)

- 使用 verilog HDL 进行计数器设计(1)

- 使用 verilog HDL 进行计数器设计

- 计数器 +1 python (1)

- 正计数器python(1)

📜 Verilog环形计数器

📅 最后修改于: 2021-01-11 15:11:03 🧑 作者: Mango

Verilog环形计数器

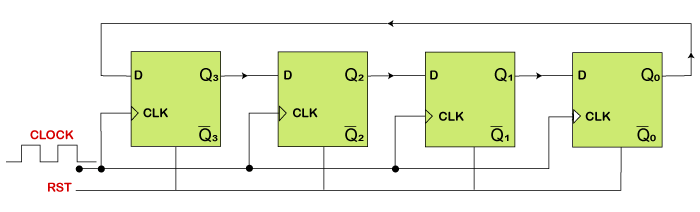

环形计数器是一种数字电路,具有以反馈方式连接的一系列触发器。环形计数器由移位寄存器组成。只要施加了时钟脉冲,数据模式就会重新循环。

该电路是一种特殊类型的移位寄存器,其中最后一个触发器的输出被反馈到第一个触发器的输入。当电路复位时,除了其中一个触发器输出外,所有其他输出均设为零。对于n触发器环形计数器,我们有一个MOD-n计数器。这意味着计数器具有n个不同的状态。

例如,如果我们使用4位环形计数器,则数据模式将每四个时钟脉冲重复一次。如果格式为1000,则将生成0100、0010、0001、1000等。

例

module ring_ctr #(parameter WIDTH=4)

(

input clk,

input rstn,

output reg [WIDTH-1:0] out

);

always @ (posedge clk) begin

if (!rstn)

out <= 1;

else begin

out[WIDTH-1] <= out[0];

for (int i = 0; i < WIDTH-1; i=i+1) begin

out[i] <= out[i+1];

end

end

end

endmodule

试验台

module tb;

parameter WIDTH = 4;

reg clk;

reg rstn;

wire [WIDTH-1:0] out;

ring_ctr u0 (.clk (clk),

.rstn (rstn),

.out (out));

always #10 clk = ~clk;

initial begin

{clk, rstn} <= 0;

$monitor ("T=%0t out=%b", $time, out);

repeat (2) @(posedge clk);

rstn <= 1;

repeat (15) @(posedge clk);

$finish;

end

endmodule

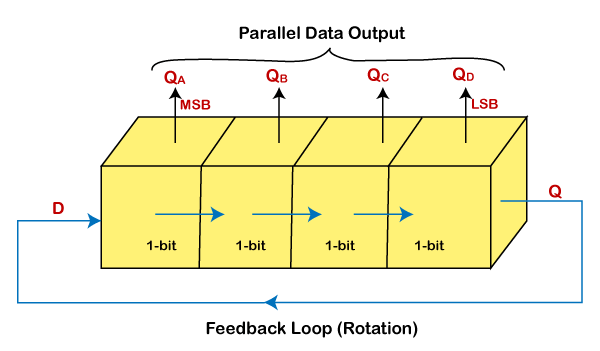

环形计数器的旋转运动

由于上述示例具有四个不同的状态,因此也称为modulo-4或mod-4计数器,每个触发器输出的频率值等于主时钟频率的四分之一。

计数器的MODULO或MODULUS是计数器在重复自身之前对其进行计数或序列化的状态数,并且可以使环形计数器输出任何模数。

Mod-n环形计数器将需要连接n个触发器,以循环提供n个不同输出状态的单个数据位。

在上面的示例中,仅使用了可能的16种状态中的4种,这使得环形计数器在其输出状态使用中效率非常低下。