📌 相关文章

- Verilog 4位计数器

- Verilog 4位计数器(1)

- Verilog Mod-N计数器(1)

- Verilog Mod-N计数器

- Verilog灰色计数器(1)

- Verilog灰色计数器

- Verilog环形计数器(1)

- Verilog环形计数器

- Verilog D闩锁

- Verilog D闩锁(1)

- Verilog Johnson计数器

- Verilog Johnson计数器(1)

- 角材料7-波纹(1)

- 角材料7-波纹

- 波纹效果 JavaScript

- 波纹效果 JavaScript(1)

- Verilog数组(1)

- Verilog数组

- Verilog函数

- Verilog函数(1)

- 更改波纹颜色 android (1)

- 使用 verilog HDL 进行计数器设计(1)

- 使用 verilog HDL 进行计数器设计

- 正计数器python(1)

- python中的计数器(1)

- 计数器 +1 python (1)

- 计数器 javascript (1)

- Verilog模块(1)

- Verilog模块

📜 Verilog波纹计数器

📅 最后修改于: 2021-01-11 15:10:08 🧑 作者: Mango

Verilog波纹计数器

纹波计数器是一个异步计数器,其中前一个触发器的输出为除第一个触发器之外的所有触发器提供时钟。

异步意味着电路的所有元件都没有公共时钟。例如,一个4位计数器的计数从0000到1111。

设计

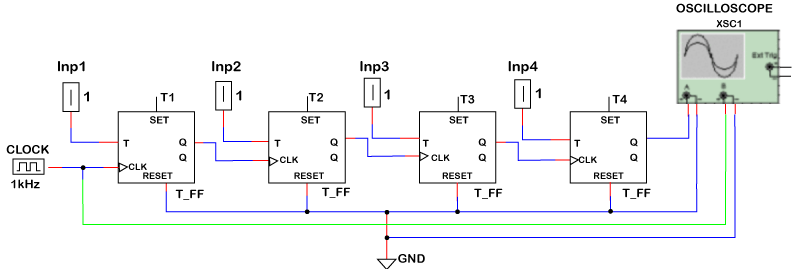

我们将向第一个T型触发器提供1Khz时钟信号,其余三个触发器的时钟将来自前一个触发器的输出(Q)。请参见下面的示意图:

上面的电路包含4个T触发器,因为我们需要4位纹波计数器。 T1的时钟由1Khz的数字源提供,其余的触发器使用以前的触发器输出作为时钟。

所有T个触发器的输入T为高电平(1),因此T触发器在每个时钟沿都切换输入。

例

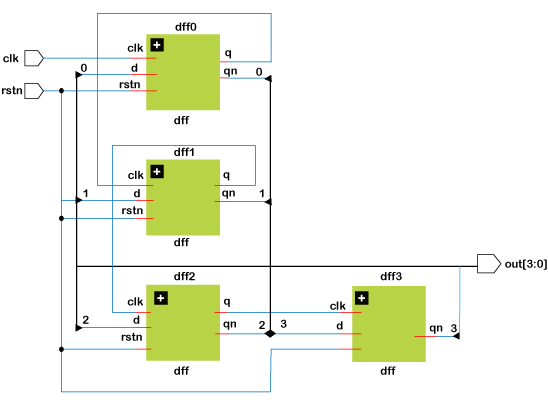

我们将执行三个模块来实现此计数器。第一个模块是执行主程序。第二个模块用于实现T触发器逻辑,第三个模块用于实现D触发器逻辑。

module dff (input d,

input clk,

input rstn,

output reg q,

output qn);

always @ (posedge clk or negedge rstn)

if (!rstn)

q <= 0;

else

q <= d;

assign qn = ~q;

endmodule

module ripple ( input clk,

input rstn,

output [3:0] out);

wire q0;

wire qn0;

wire q1;

wire qn1;

wire q2;

wire qn2;

wire q3;

wire qn3;

dff dff0 ( .d (qn0),

.clk (clk),

.rstn (rstn),

.q (q0),

.qn (qn0));

dff dff1 ( .d (qn1),

.clk (q0),

.rstn (rstn),

.q (q1),

.qn (qn1));

dff dff2 ( .d (qn2),

.clk (q1),

.rstn (rstn),

.q (q2),

.qn (qn2));

dff dff3 ( .d (qn3),

.clk (q2),

.rstn (rstn),

.q (q3),

.qn (qn3));

assign out = {qn3, qn2, qn1, qn0};

endmodule

硬件原理图

试验台

module tb_ripple;

reg clk;

reg rstn;

wire [3:0] out;

ripple r0 ( .clk (clk),

.rstn (rstn),

.out (out));

always #5 clk = ~clk;

initial begin

rstn <= 0;

clk <= 0;

repeat (4) @ (posedge clk);

rstn <= 1;

repeat (25) @ (posedge clk);

$finish;

end

endmodule