先决条件–数字逻辑中的多路复用器

问题 :

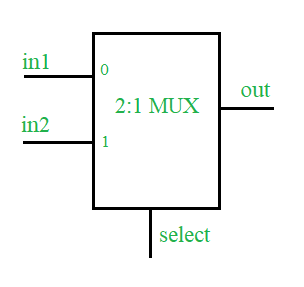

设计2:1 MUX Verilog硬件描述语言以及Testbench。

概念:

多路复用器是数字电路的组合类型,用于将可用输入线之一传送到单个输出,并且必须将哪个输入传送到输出,这将由选择线信号的值决定。 2:1多路复用器具有两个输入,一个选择线(用于选择两个输入之一)和一个输出。

真相表–

| select | out |

|---|---|

| 0 | in1 |

| 1 | in2 |

2:1 MUX的Verilog HDL代码:

设计 –

// define a module for the design

module mux2_1(in1, in2, select, out);

// define input port

input in1, in2, select;

// define the output port

output out;

// assign one of the inputs to the output based upon select line input

assign out = select ? in2 : in1;

endmodule :mux2_1

试验台 –

module test;

reg in1, in2, select;

wire out;

// design under test

mux2_1 mux(.in1(in1), .in2(in2),

.select(select), .out(out));

// list the input to the design

initial begin in1=1'b0;in2=1'b0;select=1'b0;

#2 in1=1'b1;

#2 select=1'b1;

#2 in2=1'b1;

#2 $stop();

end

// monitor the ouput whenever any of the input changes

initial begin $monitor("time=%0d, input1=%b, input2=%b,

select line=%b, output=%b", $time,

in1, in2, select, out);

end

endmodule :test

预期产出–

time=0, input1=0, input2=0, select line=0, out=0

time=2, input1=1, input2=0, select line=0, out=1

time=4, input1=1, input2=0, select line=1, out=0

time=6, input1=1, input2=1, select line=1, out=1