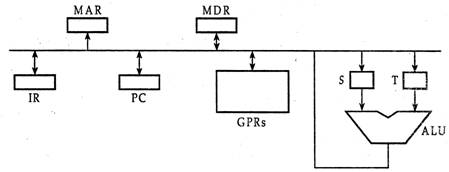

考虑以下 CPU 的数据路径。

ALU、总线和数据路径中的所有寄存器的大小相同。所有操作包括 PC 和 GPR 的增量都将在 ALU 中执行。内存读取操作需要两个时钟周期——第一个用于在 MAR 中加载地址,下一个用于将数据从内存总线加载到 MDR

79.

指令“call Rn, sub”是一个两字指令。假设 PC 在指令的第一个字的取指周期内递增,其寄存器传输解释为

Rn < = PC + 1;

PC < = M[PC]; 该指令执行周期所需的最小CPU时钟周期数为:

(一) 2

(乙) 3

(三) 4

(四) 5答案:(乙)

说明:一个周期增加PC,一个周期将PC加载到MAR,一个周期获取内存内容并加载到PC。这个问题的测验