- 组合和顺序电路

- 组合电路和顺序电路的分类

- 组合电路和顺序电路的分类

- 组合电路和顺序电路的分类(1)

- 组合电路和顺序电路的分类(1)

- 组合电路和顺序电路特性的区别(1)

- 组合电路和顺序电路特性的区别(1)

- 组合电路和顺序电路特性的区别

- 组合电路和顺序电路特性的区别

- 组合电路和顺序电路特性的区别

- 组合电路

- 组合电路(1)

- 电路 - 定义、组件、带灯泡的电路

- 电路 - 定义、组件、带灯泡的电路(1)

- 使用 Prolog 的电路(组合和顺序)实现

- 算术电路

- 算术电路(1)

- 算术电路(1)

- 算术电路(1)

- 算术电路

- 算术电路

- 计算机网络中的虚电路(1)

- 计算机网络中的虚电路

- 树遍历(顺序,预顺序和后顺序)

- 树遍历-顺序,前顺序和后顺序

- 树遍历-顺序,前顺序和后顺序(1)

- 树遍历(顺序,预顺序和后顺序)(1)

- 数字组合电路(1)

- 数字组合电路

📅 最后修改于: 2020-12-30 06:48:38 🧑 作者: Mango

介绍

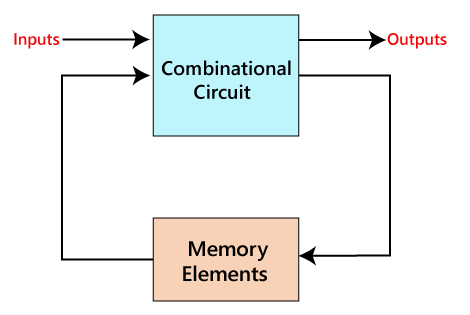

在前面的部分中,我们了解了组合电路及其工作原理。组合电路具有一组输出,这仅取决于当前的输入组合。下面是同步逻辑电路的框图。

时序电路是一种特殊的电路,具有一系列输入和输出。时序电路的输出取决于当前输入和先前输出的组合。先前的输出被视为当前状态。因此,时序电路包含组合电路及其存储器存储元件。顺序电路不必总是包含组合电路。因此,时序电路只能包含存储元件。

组合电路和时序电路之间的区别如下:

| Combinational Circuits | Sequential Circuits | |

|---|---|---|

| 1) | The outputs of the combinational circuit depend only on the present inputs. | The outputs of the sequential circuits depend on both present inputs and present state(previous output). |

| 2) | The feedback path is not present in the combinational circuit. | The feedback path is present in the sequential circuits. |

| 3) | In combinational circuits, memory elements are not required. | In the sequential circuit, memory elements play an important role and require. |

| 4) | The clock signal is not required for combinational circuits. | The clock signal is required for sequential circuits. |

| 5) | The combinational circuit is simple to design. | It is not simple to design a sequential circuit. |

时序电路的类型

异步时序电路

异步时序电路不使用时钟信号。异步电路通过脉冲进行操作。因此,输入的变化可以改变电路的状态。异步电路不使用时钟脉冲。更改输入变量时,将更改内部状态。无时钟触发器或延时触发器是异步时序电路的存储元件。异步时序电路类似于带反馈的组合电路。

同步时序电路

在同步时序电路中,存储元件状态的同步由时钟信号完成。输出存储在触发器或锁存器(存储器设备)中。仅通过时钟信号的负沿或仅通过正沿来完成输出的同步。

时钟信号和触发

时钟信号

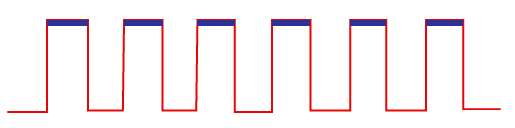

时钟信号是周期信号,其中接通时间和断开时间不必相同。当时钟信号的ON时间和OFF时间相同时,使用方波来表示时钟信号。下图显示了时钟信号:

时钟信号被视为方波。有时,信号在相等的时间内停留在逻辑上(高5V或低0V)。它会重复一定的时间,等于“开启时间”或“关闭时间”的两倍。

触发类型

这是时序电路中的两种触发类型:

电平触发

逻辑高和逻辑低是时钟信号中的两个电平。在电平触发中,当时钟脉冲处于特定电平时,才激活电路。级别触发有以下几种类型:

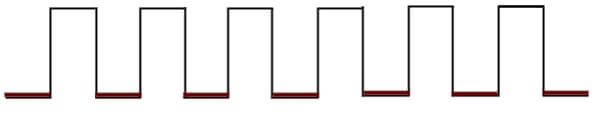

正电平触发

在正电平触发中,出现逻辑高电平的信号。因此,在该触发中,电路以这种类型的时钟信号进行操作。下面是正电平触发的示意图:

负电平触发

在负电平触发中,出现逻辑低电平信号。因此,在该触发中,电路以这种类型的时钟信号进行操作。下面是负电平触发图:

边沿触发

在边沿触发的时钟信号中,发生两种类型的转换,即,从逻辑低到逻辑高或从逻辑高到逻辑低的转换。

根据时钟信号的转换,有以下几种类型的边沿触发:

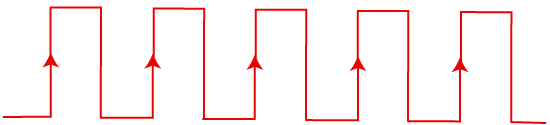

上升沿触发

从逻辑低到逻辑高的转变发生在上升沿触发的时钟信号中。因此,在上升沿触发中,电路将使用此类时钟信号进行操作。正边沿触发图如下所示。

负边沿触发

从逻辑高到逻辑低的转变发生在负沿触发的时钟信号中。因此,在负沿触发中,电路以这种类型的时钟信号进行操作。负边沿触发图如下所示。