- 数字电路-代码(1)

- 数字电路-代码

- 数字电路教程(1)

- 数字电路教程

- 讨论数字电路

- 讨论数字电路(1)

- 数字电路-逻辑门(1)

- 数字电路-逻辑门

- 数字电路-数字系统

- 数字电路-数字系统(1)

- 计数器 +1 python (1)

- 正计数器python(1)

- python中的计数器(1)

- 数字电路-K-Map方法(1)

- 数字电路-K-Map方法

- 计数器 javascript (1)

- 数字电路-触发器

- 数字电路-触发器(1)

- 数字电路-基本转换(1)

- 数字电路-基本转换

- java中的计数器(1)

- Python中的计数器 |设置 2(访问计数器)(1)

- Python中的计数器 |设置 2(访问计数器)

- 正计数器python代码示例

- python代码示例中的计数器

- 计数器 +1 python 代码示例

- 计数器 javascript 代码示例

- 数字电路-编码器(1)

- 数字电路-编码器

📅 最后修改于: 2021-01-08 05:57:37 🧑 作者: Mango

在前两章中,我们讨论了使用D触发器的各种移位寄存器和计数器。现在,让我们讨论使用T型触发器的各种计数器。我们知道,T触发器会在时钟信号的每个正沿或时钟信号的负沿切换输出。

“ N”位二进制计数器由“ N”个T触发器组成。如果计数器从0到2 -1计数,则称为二进制向上计数器。同样,如果计数器从2 × − 1递减到0,则称为二进制递减计数器。

基于触发器的计数器有两种类型,它们可以同步连接或不同步连接。

- 异步计数器

- 同步计数器

异步计数器

如果触发器未接收到相同的时钟信号,则该计数器称为异步计数器。系统时钟的输出仅作为时钟信号施加到第一触发器。其余触发器从其前一级触发器的输出接收时钟信号。因此,所有触发器的输出不会同时改变(影响)。

现在,让我们一一讨论以下两个计数器。

- 异步二进制递增计数器

- 异步二进制递减计数器

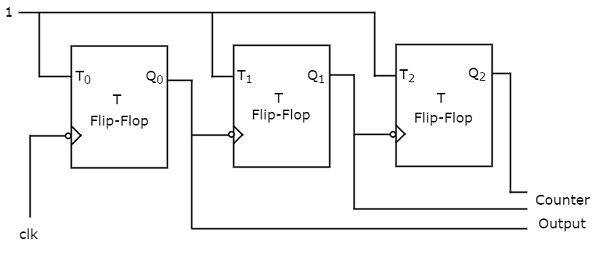

异步二进制加计数器

一个“ N”位异步二进制加计数器由“ N”个T触发器组成。它的计数范围是0到2 -1 。下图显示了3位异步二进制向上计数器的框图。

3位异步二进制加计数器包含三个T触发器,所有触发器的T输入都连接到“ 1”。所有这些触发器均为负沿触发,但输出异步变化。时钟信号直接施加到第一T触发器。因此,第一T触发器的输出在时钟信号的每个负沿触发。

第一T触发器的输出被用作第二T触发器的时钟信号。因此,第二T触发器的输出针对第一T触发器的输出的每个负沿进行切换。类似地,由于第二T触发器的输出充当第三T触发器的时钟信号,因此第三T触发器的输出针对第二T触发器的输出的每个负沿触发。

假设从最右到最左的T个触发器的初始状态为$ Q_ {2} Q_ {1} Q_ {0} = 000 $。这里,$ Q_ {2} $和$ Q_ {0} $分别是MSB和LSB。我们可以从下表了解3位异步二进制计数器的工作原理。

| No of negative edge of Clock | Q0(LSB) | Q1 | Q2(MSB) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 |

| 2 | 0 | 1 | 0 |

| 3 | 1 | 1 | 0 |

| 4 | 0 | 0 | 1 |

| 5 | 1 | 0 | 1 |

| 6 | 0 | 1 | 1 |

| 7 | 1 | 1 | 1 |

在这里,$ Q_ {0} $在时钟信号的每个负沿都进行切换。对于从1到0的每个$ Q_ {0} $,$ Q_ {1} $切换一次,否则保持先前的状态。类似地,对于从1到0的每个$ Q_ {1} $,$ Q_ {2} $切换一次,否则保持先前的状态。

在没有时钟信号的情况下,T触发器的初始状态为$ Q_ {2} Q_ {1} Q_ {0} = 000 $。对于时钟信号的每个负沿,该值递增1,并在时钟信号的第7个负沿时达到最大值。当施加时钟信号的其他负沿时,会重复此模式。

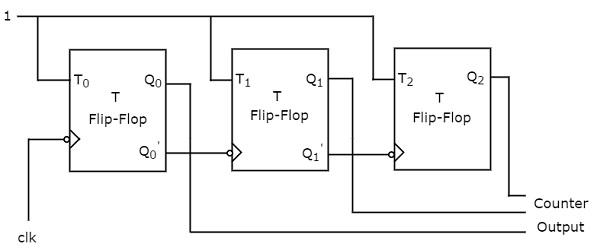

异步二进制递减计数器

一个“ N”位异步二进制递减计数器由“ N”个T触发器组成。它的计数范围是2 × -1至0。下图显示了3位异步二进制递减计数器的框图。

3位异步二进制递减计数器的框图类似于3位异步二进制递减计数器的框图。但是,唯一的区别是,不是将一级触发器的正常输出作为下一级触发器的时钟信号连接,而是将一级触发器的互补输出作为下一级触发器的时钟信号连接。互补输出从1到0与正常输出从0到1相同。

假设从最右到最左的T个触发器的初始状态为$ Q_ {2} Q_ {1} Q_ {0} = 000 $。这里,$ Q_ {2} $和$ Q_ {0} $分别是MSB和LSB。我们可以理解3位异步二进制的工作下,从下表计数器。

| No of negative edge of Clock | Q0(LSB) | Q1 | Q2(MSB) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 |

| 2 | 0 | 1 | 1 |

| 3 | 1 | 0 | 1 |

| 4 | 0 | 0 | 1 |

| 5 | 1 | 1 | 0 |

| 6 | 0 | 1 | 0 |

| 7 | 1 | 0 | 0 |

在这里,$ Q_ {0} $在时钟信号的每个负沿都进行切换。每从0到1的$ Q_ {0} $切换$ Q_ {1} $,否则保持先前的状态。类似地,每从0到1的$ Q_ {1} $切换$ Q_ {2} $,否则保持先前的状态。

在没有时钟信号的情况下,T触发器的初始状态为$ Q_ {2} Q_ {1} Q_ {0} = 000 $。对于时钟信号的每个负沿,此值减一,并在时钟信号的第8个负沿时达到相同的值。当施加时钟信号的其他负沿时,会重复此模式。

同步计数器

如果所有触发器都接收相同的时钟信号,则该计数器称为“同步计数器” 。因此,所有触发器的输出同时改变(影响)。

现在,让我们一一讨论以下两个计数器。

- 同步二进制递增计数器

- 同步二进制递减计数器

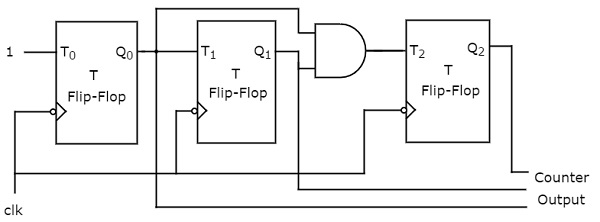

同步二进制加计数器

一个“ N”位同步二进制加计数器由“ N”个T触发器组成。它的计数范围是0到2 -1 。下图显示了3位同步二进制向上计数器的框图。

3位同步二进制加计数器包含三个T触发器和一个2输入与门。所有这些触发器均由负沿触发,并且触发器的输出同步变化(影响)。第一,第二和第三触发器的T输入分别为1,$ Q_ {0} $和$ Q_ {1} Q_ {0} $。

第一个T触发器的输出在时钟信号的每个负沿触发。如果$ Q_ {0} $为1,则第二个T触发器的输出针对时钟信号的每个负沿触发。如果两个$ Q_ {0} $,则第二个T触发器的输出针对时钟信号的每个负沿触发。 &$ Q_ {1} $是1。

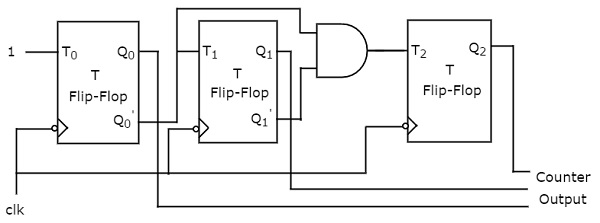

同步二进制递减计数器

“ N”位同步二进制递减计数器由“ N”个T触发器组成。它的计数范围是2 × -1到0。3位同步二进制递减计数器的框图如下图所示。

3位同步二进制递减计数器包含三个T触发器和一个2输入与门。所有这些触发器均由负沿触发,并且触发器的输出同步变化(影响)。第一,第二和第三触发器的T输入分别为1,$ {Q_ {0}}’$&’$ {Q_ {1}}’$$ {Q_ {0}}’$。

第一个T触发器的输出在时钟信号的每个负沿触发。如果$ {Q_ {0}}’$为1,则第二个T触发器的输出在时钟信号的每个负沿触发。如果两个$ {Q_ {1}}’$&$ {Q_ {0}}’$为1。