- 数字电路-触发器的转换(1)

- 数字电路-触发器的转换

- 数字电路-闩锁

- 数字电路-代码(1)

- 数字电路-代码

- 数字电路教程

- 数字电路教程(1)

- 讨论数字电路

- 讨论数字电路(1)

- 数字电路-逻辑门(1)

- 数字电路-逻辑门

- 数字电路-数字系统

- 数字电路-数字系统(1)

- 数字电路-K-Map方法(1)

- 数字电路-K-Map方法

- 数字电路-计数器

- 数字电路-基本转换

- 数字电路-基本转换(1)

- 数字电路-编码器

- 数字电路-编码器(1)

- 触发器 - SQL (1)

- SQL |触发器(1)

- SQL |触发器

- 数字电路-有用的资源(1)

- 数字电路-有用的资源

- 数字电路-解码器(1)

- 数字电路-解码器

- 数字电路-多路复用器(1)

- 数字电路-多路复用器

📅 最后修改于: 2021-01-08 05:53:38 🧑 作者: Mango

在上一章中,我们讨论了闩锁。这些是触发器的基本构建块。我们可以用两种方法实现触发器。

在第一种方法中,以这样一种方式级联两个锁存器:对每个正时钟脉冲启用第一个锁存器,对每个负时钟脉冲启用第二个锁存器。这样这两个锁存器的组合就变成了触发器。

在第二种方法中,我们可以直接实现对边缘敏感的触发器。在本章中,让我们讨论使用第二种方法的以下触发器。

- SR触发器

- D触发器

- JK触发器

- T型触发器

SR触发器

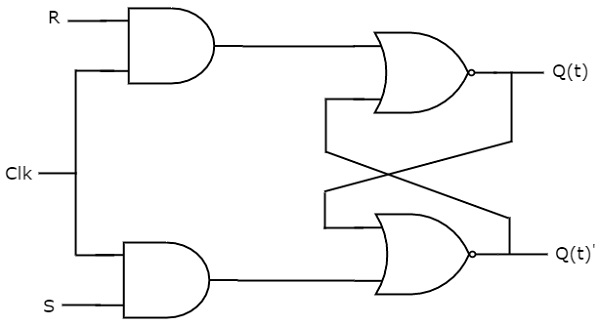

SR触发器仅在正时钟转换或负时钟转换下工作。 SR锁存器通过使能信号工作。 SR触发器的电路图如下图所示。

该电路具有两个输入S和R和两个输出Q(t)和Q(t)’。 SR触发器的操作类似于SR锁存器。但是,该触发器仅在施加时钟信号的正跳变而不是主动使能时才影响输出。

下表显示了SR触发器的状态表。

| S | R | Q(t + 1) |

|---|---|---|

| 0 | 0 | Q(t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | – |

在此,Q(t)和Q(t + 1)分别是当前状态和下一状态。因此,当施加时钟信号的正跳变时,SR触发器可用于这三个功能之一,例如基于输入条件的保持,复位和设置。下表显示了SR触发器的特性表。

| Present Inputs | Present State | Next State | |

|---|---|---|---|

| S | R | Q(t) | Q(t + 1) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | x |

| 1 | 1 | 1 | x |

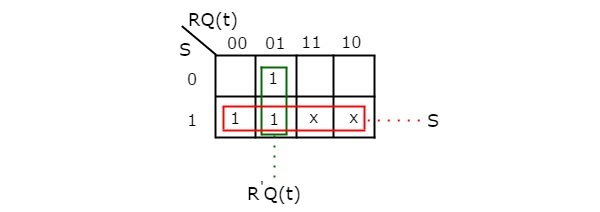

通过使用三个变量K-Map,我们可以获得下一个状态Q(t + 1)的简化表达式。下图显示了下一个状态的三个变量K-Map Q(t + 1)。

图中已显示了相邻组的最大可能分组。因此,下一状态Q(t + 1)的简化表达式为

$ Q \ left(t + 1 \ right)= S + {R}’Q \ left(t \ right)$

D触发器

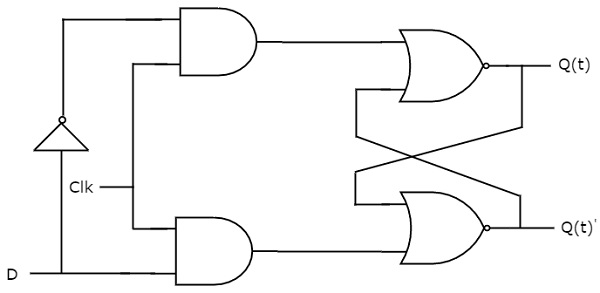

D触发器仅在正时钟转换或负时钟转换下工作。而D锁存器通过使能信号工作。这意味着,D触发器的输出对输入D的变化不敏感,除了时钟信号的有效过渡。下图显示了D触发器的电路图。

该电路具有单个输入D和两个输出Q(t)和Q(t)’。 D触发器的操作类似于D锁存器。但是,该触发器仅在施加时钟信号的正跳变而不是主动使能时才影响输出。

下表显示了D触发器的状态表。

| D | Qt + 1t + 1 |

|---|---|

| 0 | 0 |

| 1 | 1 |

因此,D触发器始终保持信息,该信息可在数据输入D上获得,时钟信号为较早的正跳变。从上面的状态表中,我们可以直接将下一个状态方程写为

Q(t +1)= D

D触发器的下一个状态始终等于数据输入,对于时钟信号的每个正向跃迁,D都等于D。因此,D触发器可用于寄存器,移位寄存器和一些计数器中。

JK触发器

JK触发器是SR触发器的修改版本。它仅在正时钟转换或负时钟转换下运行。 JK触发器的电路图如下图所示。

该电路具有两个输入J和K和两个输出Q(t)和Q(t)’。 JK触发器的操作类似于SR触发器。在这里,我们将SR触发器的输入视为S = JQ(t)’和R = KQ(t) ,以便将修改后的SR触发器用于4种输入组合。

下表显示了JK触发器的状态表。

| J | K | Q(t + 1) |

|---|---|---|

| 0 | 0 | Q(t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Q(t)’ |

在此,Q(t)和Q(t + 1)分别是当前状态和下一状态。因此,当施加时钟信号的正跳变时,JK触发器可用于这四个功能之一,例如基于输入条件的当前状态的保持,复位,设置和补码。下表显示了JK触发器的特性表。

| Present Inputs | Present State | Next State | |

|---|---|---|---|

| J | K | Q(t) | Q(t+1) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

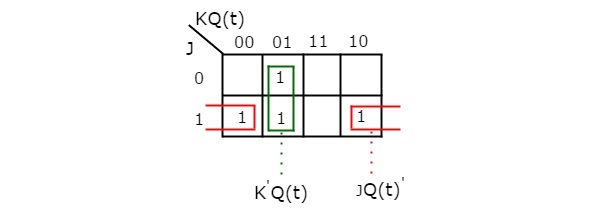

通过使用三个变量K-Map,我们可以获得下一个状态Q(t + 1)的简化表达式。下图显示了下一个状态的三个变量K-Map Q(t + 1)。

图中已显示了相邻组的最大可能分组。因此,下一状态Q(t + 1)的简化表达式为

$$ Q \ left(t + 1 \ right)= J {Q \ left(t \ right)}’+ {K}’Q \ left(t \ right)$$

T型触发器

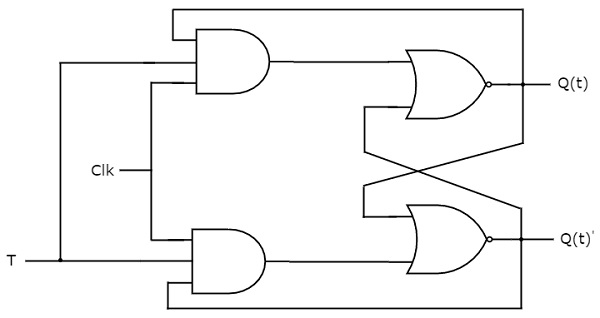

T触发器是JK触发器的简化版本。通过将相同的输入“ T”连接到JK触发器的两个输入获得。它仅在正时钟转换或负时钟转换下运行。 T触发器的电路图如下图所示。

该电路具有单个输入T和两个输出Q(t)和Q(t)’。 T触发器的操作与JK触发器的操作相同。在这里,我们将JK触发器的输入视为J = T和K = T ,以便将修改后的JK触发器用于2种输入组合。因此,我们消除了J&K的其他两个组合,在T触发器中,这两个值彼此互补。

下表显示了T型触发器的状态表。

| D | Q(t + 1) |

|---|---|

| 0 | Q(t) |

| 1 | Q(t)’ |

在此,Q(t)和Q(t + 1)分别是当前状态和下一状态。因此,当施加时钟信号的正跳变时,T触发器可用于这两个功能之一,例如基于输入条件的当前状态的保持和补码。下表显示了T触发器的特性表。

| Inputs | Present State | Next State |

|---|---|---|

| T | Q(t) | Q(t + 1) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

从上面的特性表中,我们可以直接将下一个状态方程写为

$$ Q \ left(t + 1 \ right)= {T}’Q \ left(t \ right)+ TQ {\ left(t \ right)}’$$

$$ \ Rightarrow Q \ left(t + 1 \ right)= T \ oplus Q \ left(t \ right)$$

当输入T保持逻辑高电平(1)时,T触发器的输出始终在时钟信号的每个正跳变之间切换。因此,T触发器可用于计数器。

在本章中,我们通过提供“或非”门之间的交叉耦合来实现各种触发器。同样,您可以使用“与非”门实现这些触发器。