- 数字电路-闩锁

- 数字电路-代码

- 数字电路-代码(1)

- 数字电路教程(1)

- 数字电路教程

- 在自动编码器的编码器处添加全连接层 (1)

- 讨论数字电路(1)

- 讨论数字电路

- 在自动编码器的编码器处添加全连接层 - 无论代码示例

- 数字电路-逻辑门

- 数字电路-逻辑门(1)

- 数字电路-数字系统(1)

- 数字电路-数字系统

- 数字电路-K-Map方法

- 数字电路-K-Map方法(1)

- 标签编码器python(1)

- 数字电路-计数器

- 数字电路-触发器

- 数字电路-触发器(1)

- 数字电路-基本转换(1)

- 数字电路-基本转换

- 标签编码器python代码示例

- 数字电路-有用的资源

- 数字电路-有用的资源(1)

- 数字电路-触发器的转换(1)

- 数字电路-触发器的转换

- 多部分编码器 - Python 代码示例

- 数字电路-解码器(1)

- 数字电路-解码器

📅 最后修改于: 2021-01-08 05:48:45 🧑 作者: Mango

编码器是执行解码器反向操作的组合电路。它最多具有2 n条输入线和’n’条输出线。它将产生一个等效于输入的二进制代码,该输入为高电平有效。因此,编码器使用“ n”位对2 n条输入线进行编码。在编码器中表示启用信号是可选的。

4对2编码器

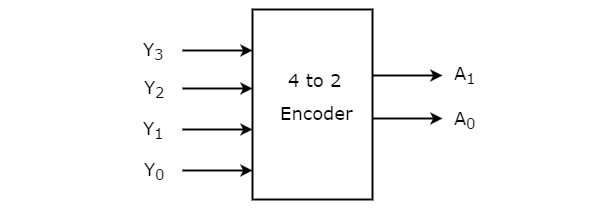

令4到2编码器具有四个输入Y 3 ,Y 2 ,Y 1和Y 0以及两个输出A 1和A 0 。下图显示了4到2编码器的框图。

在任何时候,这4个输入中只有一个可以为“ 1”,以便在输出处获得相应的二进制代码。 4至2编码器的真值表如下所示。

| Inputs | Outputs | ||||

|---|---|---|---|---|---|

| Y3 | Y2 | Y1 | Y0 | A1 | A0 |

| 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

在Truth表中,我们可以将每个输出的布尔函数写为

$$ A_ {1} = Y_ {3} + Y_ {2} $$

$$ A_ {0} = Y_ {3} + Y_ {1} $$

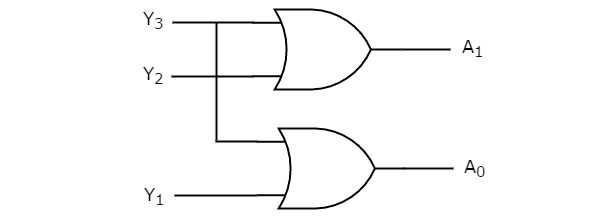

我们可以通过使用两个输入“或”门来实现上述两个布尔函数。下图显示了4到2编码器的电路图。

上面的电路图包含两个“或”门。这些“或”门用两位对四个输入进行编码

八进制到二进制编码器

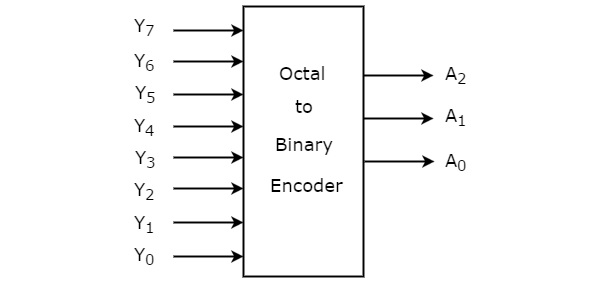

八进制到二进制编码器具有八个输入Y 7至Y 0和三个输出A 2 ,A 1和A 0 。八进制到二进制的编码器不过是8到3的编码器。下图显示了八进制到二进制编码器的框图。

在任何时候,这八个输入中只有一个可以为“ 1”,以获取相应的二进制代码。八进制到二进制编码器的真值表如下所示。

| Inputs | Outputs | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Y7 | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0 | A2 | A1 | A0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

在Truth表中,我们可以将每个输出的布尔函数写为

$$ A_ {2} = Y_ {7} + Y_ {6} + Y_ {5} + Y_ {4} $$

$$ A_ {1} = Y_ {7} + Y_ {6} + Y_ {3} + Y_ {2} $$

$$ A_ {0} = Y_ {7} + Y_ {5} + Y_ {3} + Y_ {1} $$

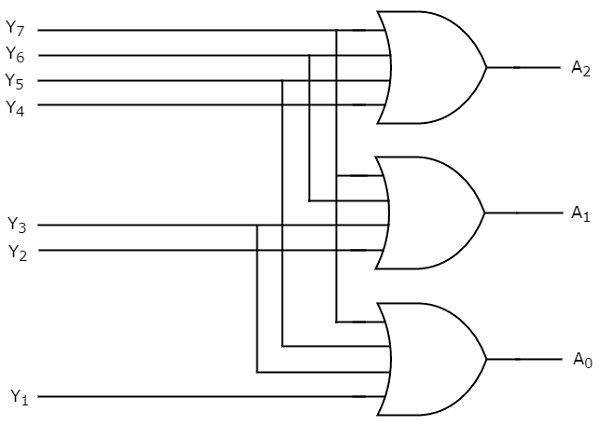

我们可以通过使用四个输入“或”门来实现上述布尔函数。八进制至二进制编码器的电路图如下图所示。

上面的电路图包含三个4输入或门。这些“或”门用三个位对八个输入进行编码。

编码器的缺点

以下是普通编码器的缺点。

-

当编码器的所有输出均等于零时,存在歧义。因为,当仅最低有效输入为一或所有输入均为零时,它可能是与输入相对应的代码。

-

如果有多个输入被激活为高电平,则编码器将产生输出,该输出可能不是正确的代码。例如,如果Y 3和Y 6均为’1’,则编码器在输出处产生111。当它为“ 1”时,既不是对应于Y 3的等效代码,当它为“ 1”时,既不是对应于Y 6的等效代码。

因此,为了克服这些困难,我们应该为编码器的每个输入分配优先级。然后,编码器的输出将是对应于有效高输入的(二进制)代码,其优先级更高。该编码器称为优先级编码器。

优先编码器

4至2优先级编码器具有四个输入Y 3 ,Y 2 ,Y 1和Y 0以及两个输出A 1和A 0 。在此,输入Y 3具有最高优先级,而输入Y 0具有最低优先级。在这种情况下,即使同时有多个输入为“ 1”,输出也将是与该输入相对应的(二进制)代码,具有更高的优先级。

为了了解输出端可用的代码是否有效,我们考虑了另外一个输出端V。

-

如果编码器的至少一个输入为“ 1”,则输出上可用的代码为有效的代码。在这种情况下,输出V将等于1。

-

如果编码器的所有输入均为“ 0”,则输出上可用的代码无效。在这种情况下,输出V将等于0。

4至2优先级编码器的真值表如下所示。

| Inputs | Outputs | |||||

|---|---|---|---|---|---|---|

| Y3 | Y2 | Y1 | Y0 | A1 | A0 | V |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | x | 0 | 1 | 1 |

| 0 | 1 | x | x | 1 | 0 | 1 |

| 1 | x | x | x | 1 | 1 | 1 |

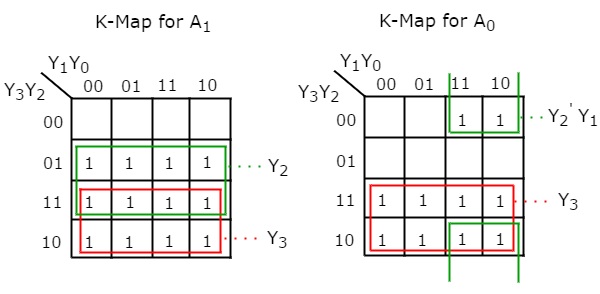

使用4个变量K映射来获取每个输出的简化表达式。

简化的布尔函数是

$$ A_ {1} = Y_ {3} + Y_ {2} $$

$ A_ {0} = Y_ {3} + {Y_ {2}}’Y_ {1} $

类似地,我们将获得输出的布尔函数V,为

$$ V = Y_ {3} + Y_ {2} + Y_ {1} + Y_ {0} $$

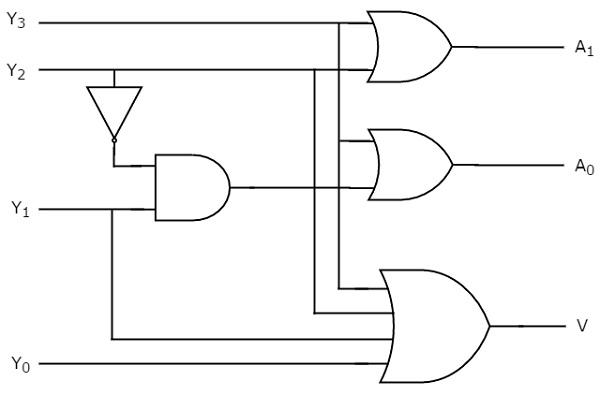

我们可以使用逻辑门来实现上述布尔函数。下图显示了4到2优先级编码器的电路图。

上面的电路图包含两个2输入或门,一个4输入或门,一个2输入与门和一个反相器。即使多个输入同时等于“ 1”,此处的“与”门和反相器组合也可用于在输出上生成有效代码。因此,该电路根据分配给每个输入的优先级用两个比特对四个输入进行编码。