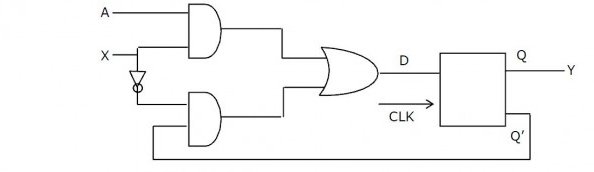

考虑以下电路,其中涉及一个正沿触发 D FF。  考虑以下时序图。设 Ai 代表第 i 个时钟周期内 A 线上的逻辑电平。

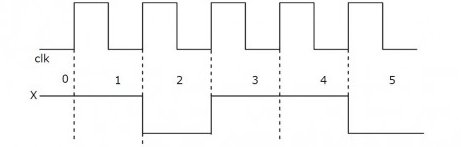

考虑以下时序图。设 Ai 代表第 i 个时钟周期内 A 线上的逻辑电平。

让 A’ 代表 A 的补码。 在时钟周期 1 到 5 内 Y 上的正确输出序列是

(A) A0 Al A1′ A3 A4

(B) A0 Al A2′ A3 A4

(C)铝 A2 A2′ A3 A4

(D) A2′ A3 A4 A5′答案:(一)

说明:这里使用的触发器是一个正沿触发的 D 触发器,这意味着只有在“时钟的上升沿”触发器才会捕获在 D 提供的输入并相应地在 Q 处给出输出。而在其他时间时钟的输出不会改变。 D触发器的输出与输入相同,即Y=Q=D(在上升沿)。

现在,在上面的问题中,给出了 5 个时钟周期,我们必须找到这些时钟周期中的输出 Q 或 Y。

首先,让我们导出逻辑门的布尔表达式。

这是:

D = AX + X’ Q’

现在,

在第一个时钟周期,(即当 t = 0 到 1 时)

这里时钟在 t=0 处有上升沿,因此此时只有 D 触发器会改变其状态。

在第一个时钟中,X = 1,所以,D = A。 现在一条逻辑线在不同的时钟周期可能有不同的电平,即可能是高电平或低电平,因此我们必须针对第 i 个时钟周期来回答 Ai 是第 i 个时钟中逻辑线 A 的逻辑电平(高或低)。

所以在第一个时钟周期,A 逻辑值应该是 A1(即第一个时钟周期的 A 值),但由于逻辑门提供的延迟(传播延迟) ,触发器使用的 A 值是之前的值A only,即它会在第 0 个时钟周期捕获使用逻辑线 A 产生的 D 值,即 A0。 X 的值也是如此,即在第 i 个时钟周期中使用 X 的先前值而不是 Xi,即 Xi-1。

现在,X 的第 1 个时钟周期值与第 0 个时钟相同,即逻辑 1。因此,X = 1,A = A0,因此,D = A0,因此 Q = Y = A0

类似地,我们必须对其他时钟周期进行处理,即不取Ai 和Xi,而是取Ai-1 和Xi-1 来获取第i 个时钟周期的输出。

在第二个时钟周期,(即当 t = 1 到 2 时)

X = 1(前一个时钟中的值),因此,D = A1(前一个时钟中的 A 值),因此 Q = Y = A1

在第 3 个时钟周期,(即当 t = 2 到 3 时)

X = 0(前一个时钟的值,见时序图),所以,D = Q’ = A1’,因此 Q = Y = A1′ (因为反馈线)

在第 4 个时钟周期,(即当 t = 3 到 4 时)

X = 1(前一个时钟中的值,),因此,D = A3,因此 Q = Y = A3

在第 5 个时钟周期,(即当 t = 4 到 5 时)

X = 1(前一个时钟中的值),因此, D = A4 ,因此 Q = Y = A4

因此输出序列是: A0 A1 A1′ A3 A4

这个问题的测验