同步数字电路系统中的时钟偏移

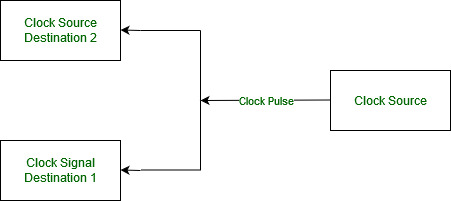

在所有逻辑元件共享相同时钟信号的同步电路中,必须将这些元件设计得尽可能靠近时钟源,因为片上系统、FPGA、CPLD 包含数十亿个晶体管。尽管这些距离由于数量庞大而非常微小,但仍存在传播延迟,这会导致时钟信号在不同时间到达芯片的不同部分。这称为时钟偏差。

在数字电路设计中,“顺序相邻”电路是指从公共源发出的脉冲应该同时到达的电路。使用这个定义,我们可以将时钟偏差的数学表达式写成

顺序相邻电路

非顺序相邻电路。

T a (时钟脉冲到达组件 a 的时间)

T b (时钟脉冲到达组件 b 的时间)

然后,

Clock skew Ts = Ta - Tb 造成时钟偏差的因素:

- 互连长度

- 温度变化

- 电容耦合

- 材料缺陷

- 时钟输入上的输入电容差异

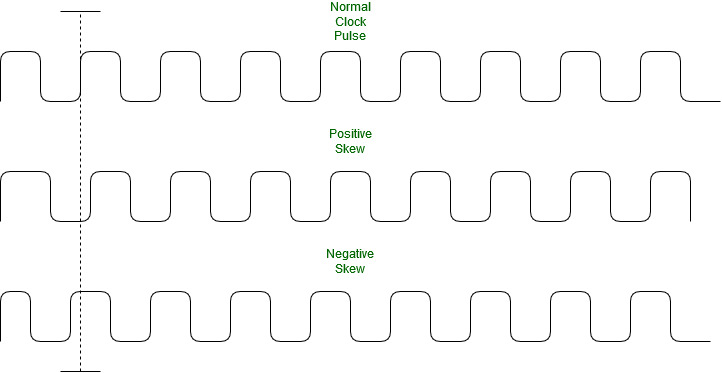

时钟偏差的类型:

- 正偏斜 –

当接收寄存器接收到的时钟脉冲晚于所需的时钟脉冲时,就会发生这种情况。 - 负偏斜 –

当接收寄存器比要求的更早接收到时钟脉冲时,就会发生这种情况。

时钟偏差的类型