- 数字电路-代码(1)

- 数字电路教程(1)

- 数字电路教程

- 讨论数字电路(1)

- 讨论数字电路

- 数字电路-逻辑门

- 数字电路-逻辑门(1)

- 数字电路-数字系统

- 数字电路-数字系统(1)

- 数字电路-K-Map方法

- 数字电路-K-Map方法(1)

- 数字电路-计数器

- 数字电路-触发器(1)

- 数字电路-触发器

- 数字电路-基本转换

- 数字电路-基本转换(1)

- 数字电路-编码器

- 数字电路-编码器(1)

- 数字电路-有用的资源(1)

- 数字电路-有用的资源

- 数字电路-触发器的转换(1)

- 数字电路-触发器的转换

- 数字电路-解码器(1)

- 数字电路-解码器

- 数字电路-多路复用器

- 数字电路-多路复用器(1)

- 数字电路-布尔代数(1)

- 数字电路-布尔代数

- 数字电路-解复用器

📅 最后修改于: 2021-01-08 05:52:47 🧑 作者: Mango

根据适合于操作的触发类型,有两种类型的存储元件。

- 锁存器

- 人字拖

锁存器对电平敏感的使能信号工作。而触发器是边缘敏感的。我们将在下一章讨论触发器。现在,让我们一一讨论SR锁存器和D锁存器。

SR锁存器

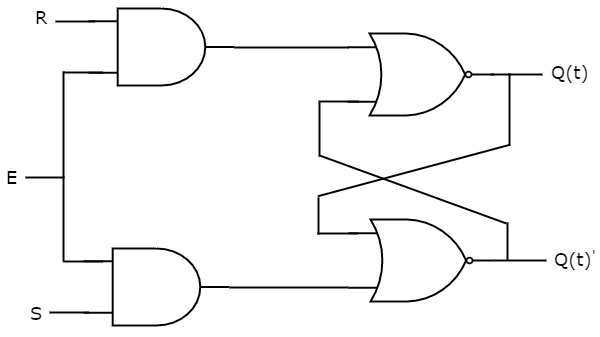

SR锁存器也称为设置复位锁存器。只要使能E保持为1,该锁存器就会影响输出。 SR锁存器的电路图如下图所示。

该电路具有两个输入S和R和两个输出Q(t)和Q(t)’。上级或非门具有两个输入R和当前状态Q(t)’的补码,并在使能E为1时产生下一个状态Q(t + 1)。

同样,下或非门具有两个输入S和当前状态Q(t),并在使能E为1时产生下一个状态Q(t + 1)’的补码。

我们知道一个2输入或非门会产生一个输出,当一个输入为0时,它是另一输入的补码。同样,当输入之一为“ 1”时,它将产生“ 0”输出。

-

如果S = 1,则下一个状态Q(t +1)等于“ 1”,而与当前状态Q(t)值无关。

-

如果R = 1,则下一个状态Q(t +1)等于“ 0”,而与当前状态Q(t)值无关。

任何时候,这两个输入中的任何一个都应该为“ 1”。如果两个输入均为“ 1”,则下一个状态Q(t + 1)值不确定。

下表显示了SR锁存器的状态表。

| S | R | Q(t + 1) |

|---|---|---|

| 0 | 0 | Q(t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | – |

因此,SR Latch根据输入条件执行三种功能,例如保持,设置和复位。

D闩锁

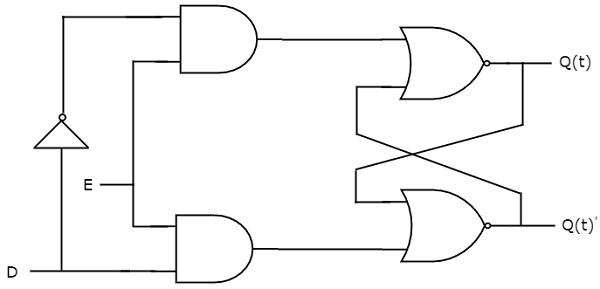

SR锁存器有一个缺点。当输入S和R均为1时,则无法预测下一个状态值。因此,我们可以通过D Latch克服这一困难。它也称为数据锁存器。 D Latch的电路图如下图所示。

该电路具有单个输入D和两个输出Q(t)和Q(t)’。 D锁存器是通过在S amp&R输入之间放置一个反相器并将D输入连接到S来从SR锁存器获得的。这意味着我们消除了S和R的组合具有相同的值。

-

如果D = 0→S = 0&R = 1,则下一个状态Q(t + 1)将等于’0’,而与当前状态Q(t)值无关。这对应于SR锁存状态表的第二行。

-

如果D = 1→S = 1&R = 0,则下一个状态Q(t + 1)将等于“ 1”,而与当前状态Q(t)值无关。这对应于SR锁存状态表的第三行。

下表显示了D锁存器的状态表。

| D | Q(t + 1) |

|---|---|

| 0 | 0 |

| 1 | 1 |

因此,D Latch保持数据输入D上可用的信息。这意味着,只要使能为高,D Latch的输出就对输入D的变化敏感。

在本章中,我们通过提供“或非”门之间的交叉耦合来实现各种锁存器。同样,您可以使用“与非”门实现这些锁存器。