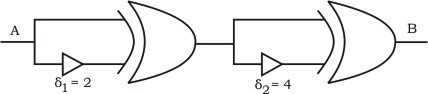

考虑以下由异或门和同相缓冲器组成的电路。

如图所示,同相缓冲器的延迟为 d1 = 2 ns 和 d2 = 4 ns。 XOR 门和所有连线都具有零延迟。假设所有门输入、输出和线路在时间 0 时稳定在逻辑电平 0。如果在输入 A 处应用以下波形,则在间隔期间 B 处发生多少次转换(逻辑电平变化)从 0 到 10 ns ? ![]()

(一) 1

(乙) 2

(三) 3

(四) 4答案: (D)

说明:当我们绘制不同输入的波形时:

- 2ns 缓冲器输入是 A 的移位形式

- 第一个 EXOR 门的输出是 1 到 3 的单拍

- 虽然这是由 4ns 缓冲区移位

- 这反过来导致第二个 EXOR 门的两个节拍输出

因此有 4 个转换,所以选项 (D) 是正确的。

这个问题的测验