计数器是计算输入出现次数的电路。该电路由触发器和组合元件组成,用于生成控制信号。

If M = Total number of states, and

n = Total number of flip-flop

Then, M <= 2n

If M = 2n ; Binary counter

and M < 2n ; Non-binary counter 非二进制计数器框图:

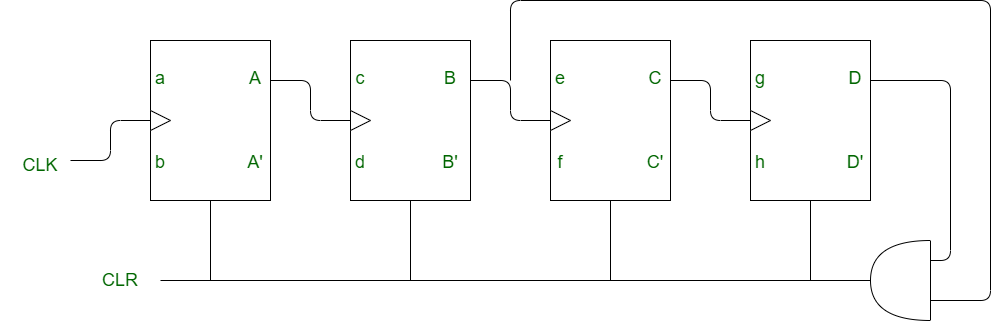

这是一个 mod-10 计数器的框图。这里,所需的触发器总数为 4,因此已使用状态数为 10,未使用状态数为 6。

为了设计一个非二进制计数器,需要一个逻辑门来检测 M 级。在 mod-10 计数器中,从 0000 到 10001 检测到 10 个阶段,一旦 1010 出现,它就会清除所有触发器。

非二进制计数器的制作:

为了制作非二进制计数器,

- 如果存在 CLR 并且 CLK 与输出 Q 连接,那么我们使用与门。

- 如果 CLR 存在并且 CLK 连接到输出 Q’,那么我们使用 NOR 门。

- 如果存在 CLR 的补码并且 CLK 连接到输出 Q,那么我们使用与非门。

- 如果存在 CLR 的补码并且 CLK 连接到输出 Q’,那么我们使用或门。

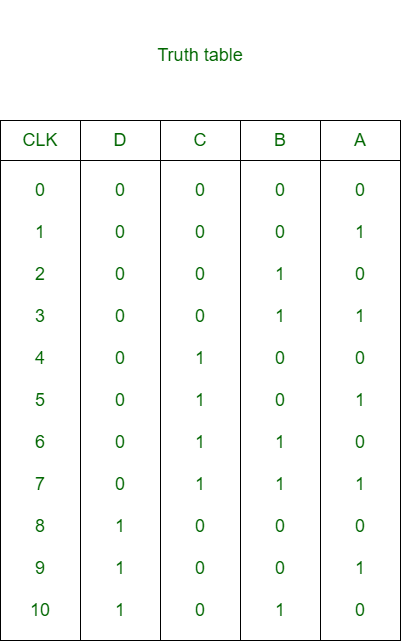

真值表:

从真值表中可以清楚地看出,一旦 1010 出现,AND 门的输入变为 11,这将用 CLR =1 复位触发器。

输出频率:

mod-M计数器的输出频率,

= f / M 如果在最后一个输出(即 D)上没有反馈,则输出频率,

= f / (2n)