先决条件 – 计数器

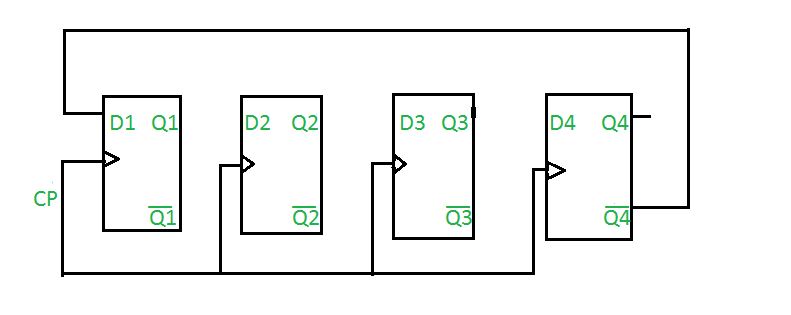

约翰逊计数器又称爬行计数器,是同步计数器的一个例子。在约翰逊计数器中,最后一个触发器的互补输出连接到第一个触发器的输入,为了实现 n 位约翰逊计数器,我们需要 n 个触发器。它是最重要的移位寄存器计数器类型之一。它是由输出反馈到自己的输入而形成的。约翰逊计数器是一个带反相的环。约翰逊计数器的别称是:爬行计数器、扭环计数器、行走计数器、移动计数器和开关尾计数器。

Total number of used and unused states in n-bit Johnson counter:

number of used states=2n

number of unused states=2n – 2*n

例子:

如果 n=4

4 位约翰逊计数器

最初,假设所有触发器都被复位。

真值表:

在哪里,

CP 是时钟脉冲和

Q1、Q2、Q3、Q4 是状态。

问题:确定 4 位约翰逊计数器中已使用和未使用状态的总数。

答案:使用状态总数= 2*n

= 2*4

= 8

未使用状态的总数= 2 n – 2*n

= 2 4 -2*4

= 8

一切都有一些优点和缺点。

约翰逊计数器的优点:

- Johnson 计数器具有相同数量的触发器,但它可以计数环形计数器可以计数的状态数量的两倍。

- 它可以使用 D 和 JK 触发器来实现。

- Johnson 环形计数器用于对连续循环中的数据进行计数。

- 约翰逊计数器是一种自解码电路。

约翰逊计数器的缺点:

- 约翰逊计数器不以二进制序列计数。

- 在约翰逊计数器中,未使用的状态数多于正在使用的状态数。

- 所需的触发器数量是时序信号数量的二分之一。

- 它可以构建为任意数量的时序。

约翰逊计数器的应用:

- Johnson 计数器用作同步十进制计数器或分频器电路。

- 它用于硬件逻辑设计以创建复杂的有限状态机。例如:ASIC 和 FPGA 设计。

- 3 级约翰逊计数器用作产生 1200 相移的 3 相方波发生器。

- 它用于通过改变反馈来划分时钟信号的频率。