考虑具有 5 个阶段的流水线处理器,指令提取 (IF)、指令解码 (ID)、执行 (EX)、内存访问 (MEM) 和回写 (WB)。除 EX 阶段外,流水线的每个阶段都需要一个周期。假设 ID 阶段只是对指令进行解码,而寄存器读取是在 EX 阶段进行的。 EX阶段ADD指令需要1个周期,寄存器读取在EX阶段进行,EX阶段ADD指令需要1个周期,MUL指令需要2个周期。忽略管道寄存器延迟。

考虑以下 8 条指令的序列:

ADD, MUL, ADD, MUL, ADD, MUL, ADD, MUL 假设每条 MUL 指令都依赖于它之前的 ADD 指令的数据,并且每个 ADD 指令(除了第一条 ADD)都依赖于它之前的 MUL 指令的数据。加速定义如下。

Speedup = (Execution time without operand forwarding) / (Execution time with operand forwarding)

在流水线处理器上执行给定指令序列(四舍五入到小数点后两位)所达到的加速比是 ____________。

(一) 1.875

(乙) 1.5625

(三) 2

(四) 1.667答案:(一)

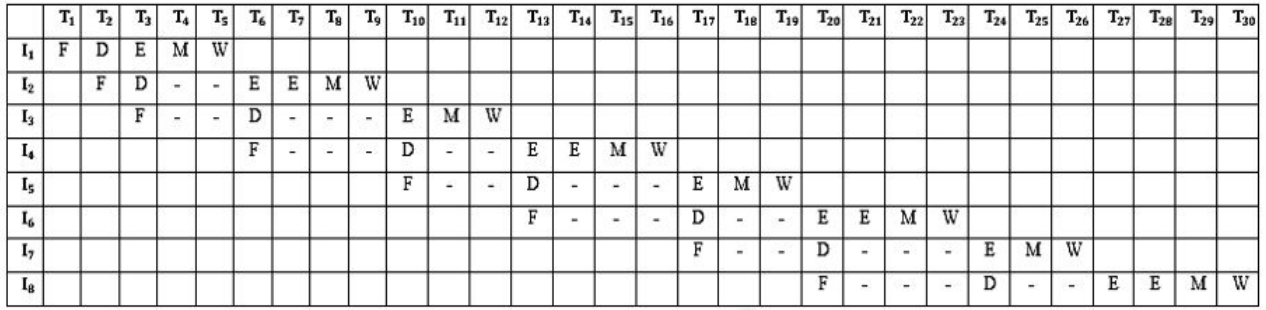

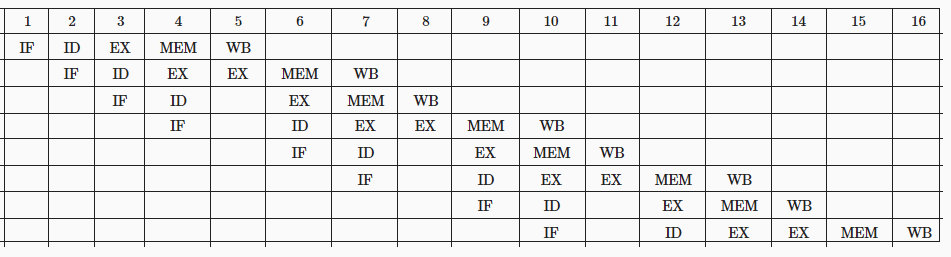

说明:给出了无操作数转发和有操作数转发的时序图

以下:

没有操作数转发:

没有操作数转发的时间 = 30

使用操作数转发:

操作数转发所用的时间 = 16

所以,

加速 = 30 /16 = 1.875这个问题的测验