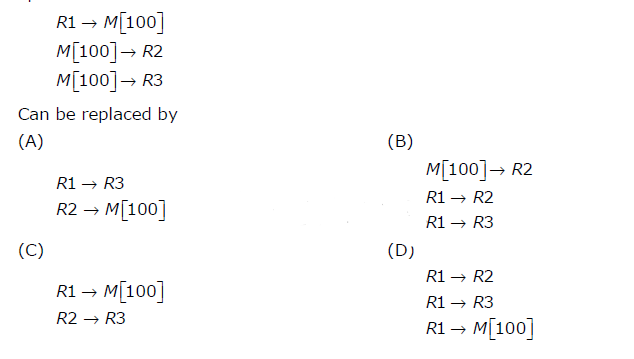

如果我们使用内部数据转发来提高CPU的性能(R1,R2和R3是寄存器,而M [100]是内存引用),则操作顺序

(A) A

(B) B

(C) C

(D) D答案: (D)

解释:

•数据转发:在图(2)中,ADD和SUB指令由于R1寄存器而与数据相关,第二条和第三条指令在ID阶段读取寄存器R1的值,但是第一条指令在WB阶段之后更新R1的值。因此,第二条SUB指令在接下来的两个周期内停顿以获取R1寄存器的更新值。

•内部数据转发是一种减少由于数据依赖性而导致的停顿的机制,它使用硬件技术将级间缓冲寄存器(IBR)的结果转发到下一条指令的缓冲寄存器。 ALU操作后(在第一条指令中)一旦结果可用,就将结果作为输入传送到ALU单元,然后ALU操作后R1的更新值可用(否则在WB饱和后可用),因此没有停顿。

• EX / MEM寄存器的ALU结果总是反馈到ALU输入锁存器。如果转发硬件检测到先前的ALU操作已写入与当前ALU操作的源相对应的寄存器,则控制逻辑会将转发的结果选择为ALU输入,而不是从寄存器文件中读取的值。

•正如Ques中给出的那样,直接从问题开始,将寄存器R1的值复制(或更确切地说是加载)到存储器位置M [100],然后将M [100]的值存储到寄存器R2和R3。选项A,B C和C是错误的,因为它们不会产生所需的结果。

•假设寄存器R1,R2,R3和存储器参考M [100]分别具有初始值10、20、30和40,然后在执行一系列操作后,寄存器R2,R3和存储器参考M [100]的初始值为10分别为10和10。

•在选项A中,执行操作后,寄存器R2,R3和存储器引用M [100]的值分别为20、10和20。在选项B中,寄存器R2,R3和存储器引用M [100]的值分别为10,10和40,而选项C,寄存器R2,R3和存储器引用M [100]的值分别为20,20和10。但是选项D产生,所有寄存器和内存引用的值均等于所需的值10,因此选项(D)仅正确。

该解决方案由Nirmal Bharadwaj提供。

这个问题的测验