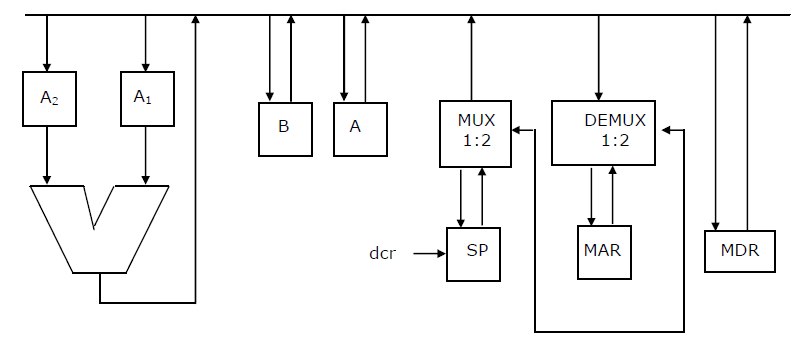

考虑以下简单非堆积 CPU 的数据路径。寄存器 A、B、A1、A2、MDR、总线和 ALU 均为 8 位宽。 SP 和 MAR 是 16 位寄存器。 MUX 的大小为 8 × (2:1),DEMUX 的大小为 8 × (1:2)。每个内存操作需要 2 个 CPU 时钟周期,并使用 MAR(内存地址寄存器)和 MDR(内存日期寄存器)。 SP 可以在本地递减。

CPU 指令“push r”,其中 = A 或 B,具有规范

M [SP]执行“push r”指令需要多少个CPU时钟周期?

(一) 1

(乙) 3

(三) 4

(四) 5答案:(乙)

说明: push ‘r’ 包含以下操作:

M[SP ]!R

SP!SP-1

‘r’ 存储在当前地址堆栈指针处的内存中,这需要 2 个时钟周期

然后 SP 递减以指向堆栈的下一个顶部

所以总周期=3

所以(B)是正确的选项

这个问题的测验