考虑以下初始状态 Q0 = Q1 = 0 的电路。 D 触发器是正沿触发,设置时间为 20 纳秒,保持时间为 0。

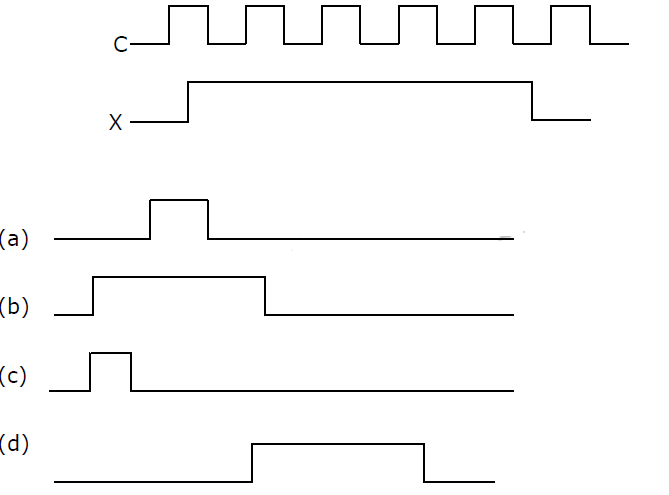

考虑以下 X 和 C 的时序图; C <= 40 纳秒的时钟周期。哪一个是 Y 的正确情节?

(一)

(乙)乙

(C) c

(D) d答案:(一)

说明:设置时间和保持时间只是为了确保边沿触发正常工作。

- 由于时钟是上升沿触发,所以第一个上升沿触发:由于 X 为 0,所以输出将为 0。另外,Q0 和 Q0’分别为 0 和 1。

- 现在,在第二步中,由于触发器的建立时间为 20 ns 且时钟周期≥ 40 ns,因此 Q0′ 将为 1。

因此,第二个上升沿触发:由于 X 为 1,Q0′ 为 1,因此输出为 1。 - 现在,Q0′ 将变为 0,但输出 Y 不会改变,因为触发器是正沿触发。

第三个上升沿触发:由于X为1,Q0′为0,所以输出为0。 - 现在,输出永远不会变回 1,因为 Q0′ 始终为 0,当 Q0′ 最终变为 1 时,X 为 0。

所以,选项(A)是正确的。

如果您发现上面的帖子有任何错误,请在下面发表评论。这个问题的测验