5 级流水线处理器具有指令提取(IF)、指令解码(ID)、操作数提取(OF)、执行操作(PO)和写操作数(WO)阶段。IF、ID、OF 和 WO 阶段占用 1 个时钟任意一条指令一个周期,PO阶段ADD和SUB指令需要1个时钟周期,MUL指令需要3个时钟周期,DIV指令需要6个时钟周期。流水线中使用操作数转发。时钟周期数是多少需要执行以下指令序列?

Instruction Meaning of instruction

I0 :MUL R2 ,R0 ,R1 R2 ¬ R0 *R1

I1 :DIV R5 ,R3 ,R4 R5 ¬ R3/R4

I2 :ADD R2 ,R5 ,R2 R2 ¬ R5+R2

I3 :SUB R5 ,R2 ,R6 R5 ¬ R2-R6 (一) 13

(乙) 15

(三) 17

(四) 19答案:(乙)

说明:操作数转发:在这种技术中,操作数的值在存储之前被赋予相关指令的相关阶段。

上题中,I2依赖于I0和I1,I3依赖于I2。

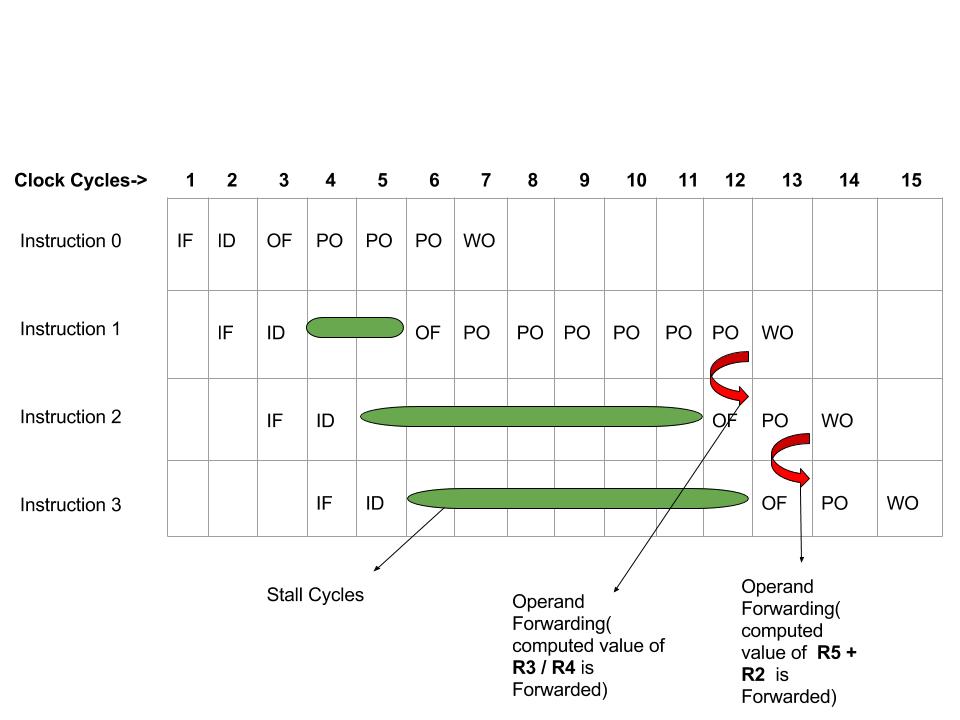

让我们用时空图来看看这个问题。

上面是一个时空图,表示指令在其中执行的流水线。

指令0是MUL操作,在PO阶段占用CPU的3个时钟周期,其他阶段只需要1个周期。

指令1是一个DIV操作,在PO阶段占用CPU的6个时钟周期,其他阶段只需要1个周期。

这里可以注意到,即使在第 4 个时钟周期 OF 阶段空闲时,也没有给它指令 1。这是一个设计问题。只有当它们将在下一个周期中被操作或执行时,才应该获取操作数,否则有数据损坏的可能性。由于 PO 阶段在下一个周期中不是空闲的,因此 OF 被延迟,并且仅在进入 PO 阶段的 1 个周期之前为指令 1 完成。

指令 2 是一个 ADD 操作,它在所有阶段占用 CPU 的 1 个时钟周期。但它是一个依赖操作。它需要指令 0 和指令 1 提供的操作数。

指令 2 需要 R5 和 R2 相加,它准时得到 R2,因为直到指令 2 到达它的 PO 阶段 R2 才会被存储在内存中。现在还需要R5,但是指令2的PO和指令1的WO是并行的。这意味着指令 2 在被指令 1 存储之前不能取 R5 的值。因此,操作数转发的概念来了。在指令 1 存储其结果/值 R5 之前,它可以先将其转发到指令 2 的 Fetch-Execute Buffer,以便指令 2 也可以与指令的 WO 阶段并行使用它。这将节省所需的额外时钟周期(如果不使用操作数转发,并且需要从内存中取出 R5)。

在指令 3 中,对指令 2 计算的 R2 的值应用了相同的操作数转发概念。

因此,操作数转发在这里节省了 2 个额外的时钟周期。 (指令 2 中的 1 个周期和指令 3 中的 1 个周期)。

所以总周期数为15,从图中可以看出,每个阶段的实例代表1个时钟周期。所以一共15个。

这个问题的测验